- ☆Networking architecture based on data-driven processor

- ☆Recent research progress: Data-driven chip multiprocessor (CUE-v3, ULP-DDCMP)

- ☆Current research topics (since 2013)

- ●Research

- ●Laboratory Equipment

●Encouragement

- ●Merits for your job hunting

- ●3 people to be accepted

- ●You are always welcomed.

Contents of the Research

Data-driven processor is the realization of a data-driven execution model in which operations become executable after all of their operands arrive. The data-driven processor can realize multiprocessing without any overheads such as context-switching which is found in sequential (von Neumann type) processors, and thus it can guarantee real-time processing even when multiplicity (e.g. the number of IP packets processed simultaneously) increases as long as the processing loads is under design target. This real-time multiprocessing feature is indispensable for networking processing in which real-time constraints are strictly demanded even when network traffic (i.e. the number of IP packets processed simultaneously) increases. That is, the data-driven processor is inherently suitable for networking processing. Based on the data-driven processor, we are now studying on networking architecture straddling multiple research fields such as networking scheme, processor architecture and circuit implementation.

CUE-v3 is a chip multiprocessor housing 4 hybrid processor core. Each core of the CUE-v3 realizes both the data-driven execution and the control-driven execution to achieve both the real-time multiprocessing and the efficient inline processing. Already, we have fabricated a VLSI chip of the CUE-v3 in a research project named “R&D on Data-driven Networking Processors Suitable for an Ad-hoc Ubiquitous Communication Environment” from 2006 to 2008. This project is supported by SCOPE (Strategic Information and Communications R&D Promotion Programme) of MIC (Ministry of Internal Affairs and Communications in Japan). The evaluation by using the fabricated CUE-v3 chip has shown that the CUE-v3 can achieve scalable performance improvement by increasing the number of cores.

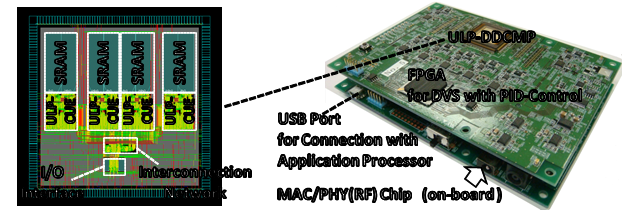

From 2007 to 2012, we have conducted a research project named "Ultra-Low-Power Data-Driven Networking System" which is commissioned by CREST (Core Research for Evolutional Science and Technology) of JST (Japan Science and Technology Agency). The purpose of this project is to realize a chip multiprocessor for realizing ultra-low-power consumption of ad hoc networking. As a result of this research, ULP-CUE (Ultra-Low-Power CUE) has been proposed by simplifying the hybrid processor core of the CUE-v3 from the viewpoint of low-power consumption, and a VLIS chip of ULP-DDCMP (Ultra-Low-Power Data-Driven Chip MultiProcessor) housing 4 ULP-CUE’s has also been fabricated. The evaluation in the project has shown that the power consumption of networking system can be reduced to 1/180 by integrating the ULP-DDCMP and our ad hoc networking scheme.The purpose of our current research is to realize a dependable networking environment that reduces the occurrence of congestion disturbing communication. In order to reduce the traffic increase which may result in the congestion, we are now developing an ad hoc network which can use both routing-based communication and broadcasting as the situation demands. This is because the routing-based communication is suitable to reduce the redundant traffic increase in the paths which are not between the source and destination nodes and the broadcasting can reduce the traffic increases caused by the control packets for routing. Our current research topics are such as (1) an ad hoc networking scheme to use the routing-based communication and broadcasting for situations and (2) a data-driven real-timed processing platform indispensable to realize the ad hoc networking scheme, but not limited to them. (Domestic and international patents pending)

ULP-DDCMP chip and its verification/evaluation board

You have a chance to research extremely unique processor and have a good experience of creation/design/verification/evaluation of the whole system straddling multiple research fields such as networking scheme, processor architecture and circuit implementation.

You can use the latest workstations and storages installed for CAD tools to design VLSI chips. Also, you have personal work space and the latest PC.

You can get a chance to publish the results of your research in not only domestic conferences but also international conferences. In this year, we have visited Las Vegas (USA) to present our results.

Three doctoral-course members in our Lab. are working also as a member of society. You don’t miss your chance to get in touch with them.

You can participate in joint R&D (Research and Development) with domestic manufacturers, and experience the processes from system specifications definition to implementation. Moreover, you can get the skills for system design and have business work experiences with relevant companies.

People who want to realize ideas are highly-welcomed.

We are ready for giving a detailed explanation about our Lab. anytime. We have two choices, short-version (15min.) and long-version (60min.) , for the detailed explanation, so you can select one of them according to your vacant time.

Please feel free to contact us, e-mail: san@cs.tsukuba.ac.jp (Shuji Sannomiya).

Copyright 2016 DDNA Lab. ALL Rights Reserved.